#### **Logic and Computer Design Fundamentals**

# **Chapter 6 – Sequential Circuits**

Part 2 - Sequential Circuit Design

#### Charles Kime & Thomas Kaminski

© 2004 Pearson Education, Inc.

Terms of Use

(Hyperlinks are active in View Show mode)

#### Overview

- Part 1

- Types of Sequential Circuits

- **Storage Elements**

- Latches

- Flip-Flops

- Sequential Circuit Analysis

- State Tables

- State Diagrams

- Part 2

- Sequential Circuit Design

- Specification

- Formulation

- State Assignment

- Flip-Flop Input and Output Equation Determination

- Optimization

- Verification

#### The Design Procedure

- Specification

- Formulation Obtain a state diagram or state table

- State Assignment Assign binary codes to the states

- Flip-Flop Input Equation Determination Select flip-flop types and derive flip-flop equations from next state entries in the table

- Output Equation Determination Derive output equations from output entries in the table

- Optimization Optimize the equations

- Technology Mapping Find circuit from equations and map to flip-flops and gate technology

- Verification Verify correctness of final design

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 3

#### **Specification**

- Component Forms of Specification

- Written description

- Mathematical description

- Hardware description language\*

- Tabular description\*

- Equation description\*

- Diagram describing operation (not just structure)\*

- Relation to Formulation

- If a specification is rigorous at the binary level (marked with \* above), then all or part of formulation may be completed

#### Formulation: Finding a State Diagram

- A state is an abstraction of the history of the past applied inputs to the circuit (including power-up reset or system reset).

- The interpretation of "past inputs" is tied to the synchronous operation of the circuit. E. g., an input value (other than an asynchronous reset) is measured only during the setup-hold time interval for an edge-triggered flip-flop.

#### Examples:

- State A represents the fact that a 1 input has occurred among the past inputs.

- State B represents the fact that a 0 followed by a 1 have occurred as the most recent past two inputs.

Logic and Computer Dealgn Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 5

#### Formulation: Finding a State Diagram

- In specifying a circuit, we use states to remember meaningful properties of past input sequences that are essential to predicting future output values.

- A <u>sequence recognizer</u> is a sequential circuit that produces a distinct output value whenever a prescribed pattern of input symbols occur in sequence, i.e, recognizes an input sequence occurence.

- We will develop a procedure specific to sequence recognizers to convert a problem statement into a state diagram.

- Next, the state diagram, will be converted to a state table from which the circuit will be designed.

#### **Sequence Recognizer Procedure**

- To develop a sequence recognizer state diagram:

- Begin in an initial state in which NONE of the initial portion of the sequence has occurred (typically "reset" state).

- Add a state that recognizes that the first symbol has occurred.

- Add states that recognize each successive symbol occurring.

- The final state represents the input sequence (possibly less the final input value) occurence.

- Add state transition arcs which specify what happens when a symbol *not* in the proper sequence has occurred.

- Add other arcs on non-sequence inputs which transition to states that represent the input subsequence that has occurred.

- The last step is required because the circuit must recognize the input sequence regardless of where it occurs within the overall sequence applied since "reset.".

Logic and Computer Design Fundamentals PowerPoint® Slides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 7

#### **State Assignment**

- Each of the m states must be assigned a unique code

- Minimum number of bits required is n such that

$$n \ge \lceil \log_2 m \rceil$$

where  $\lceil x \rceil$  is the smallest integer  $\ge x$

- There are useful state assignments that use more than the minimum number of bits

- There are 2<sup>n</sup> m unused states

### Sequence Recognizer Example

- Example: Recognize the sequence 1101

- Note that the sequence 1111101 contains 1101 and "11" is a proper sub-sequence of the sequence.

- Thus, the sequential machine must remember that the first two one's have occurred as it receives another symbol.

- Also, the sequence 1101101 contains 1101 as both an initial subsequence and a final subsequence with some overlap, i. e., <u>1101</u>101 or 110<u>1101</u>.

- And, the 1 in the middle, 1101101, is in both subsequences.

- The sequence 1101 must be recognized each time it occurs in the input sequence.

PowerPoint® Stides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 9

#### **Example: Recognize 1101**

- Define states for the sequence to be recognized:

- assuming it starts with first symbol,

- continues through each symbol in the sequence to be recognized, and

- uses output 1 to mean the full sequence has occurred,

- with output 0 otherwise.

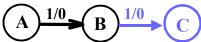

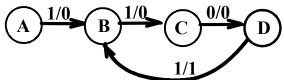

- Starting in the initial state (Arbitrarily named "A"): 1/0

- Add a state that recognizes the first "1."

- State "A" is the initial state, and state "B" is the state which represents the fact that the "first" one in the input subsequence has occurred. The output symbol "0" means that the full recognized sequence has not yet occurred.

#### **Example: Recognize 1101** (continued)

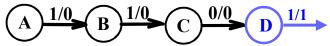

- After one more 1, we have:

- C is the state obtained when the input sequence has two "1"s.

• Finally, after 110 and a 1, we have:

- Transition arcs are used to denote the output function (Mealy Model)

- Output 1 on the arc from D means the sequence has been recognized

- To what state should the arc from state D go? Remember: 1101101?

- Note that D is the last state but the output 1 occurs for the input applied in D. This is the case when a Mealy model is assumed.

gic and Computer Design Fundamentals PowerPoint® Stides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 11

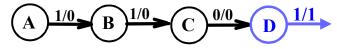

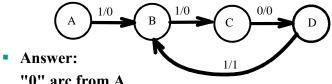

#### **Example: Recognize 1101** (continued)

Clearly the final 1 in the recognized sequence 1101 is a sub-sequence of 1101. It follows a 0 which is not a sub-sequence of 1101. Thus it should represent the same state reached from the initial state after a first 1 is observed. We obtain:

gic and Computer Dealgn Fundamentals worPoint<sup>©</sup> Slides 5 2004 Pearson Education, Inc.

#### **Example: Recognize 1101** (continued)

- The state have the following abstract meanings:

- A: No proper sub-sequence of the sequence has occurred.

- B: The sub-sequence 1 has occurred.

- C: The sub-sequence 11 has occurred.

- D: The sub-sequence 110 has occurred.

- The 1/1 on the arc from D to B means that the last 1 has occurred and thus, the sequence is recognized.

PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 13

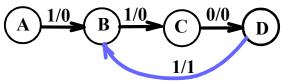

#### **Example: Recognize 1101** (continued)

The other arcs are added to each state for inputs not yet listed. Which arcs are missing?

"0" arc from A

"0" arc from B "1" arc from C

"0" arc from D.

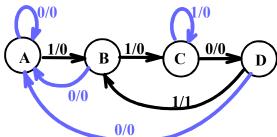

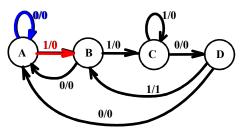

#### **Example: Recognize 1101** (continued)

State transition arcs must represent the fact that an input subsequence has occurred. Thus we get:

Note that the 1 arc from state C to state C implies that State C means two or more 1's have occurred.

PowerPoint<sup>®</sup> Stides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 15

#### **Formulation: Find State Table**

- From the State Diagram, we can fill in the State Table.

- There are 4 states, one input, and one output. We will choose the form with four rows, one for each current state.

- From State A, the 0 and 1 input transitions have been filled in along with the outputs.

| Present<br>State | Next State<br>x=0 x=1 | Output x=0 x=1 |

|------------------|-----------------------|----------------|

| A                | A B                   | 0 0            |

| В                |                       |                |

| C                |                       |                |

| D                |                       |                |

#### **Formulation: Find State Table**

• From the state diagram, we complete the state table.

0 What would the state diagram and state table look like for the Moore model?

PowerPoint<sup>®</sup> Stides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 17

#### **Example: Moore Model for Sequence 1101**

- For the Moore Model, outputs are associated with states.

- We need to add a state "E" with output value 1 for the final 1 in the recognized input sequence.

- This new state E, though similar to B, would generate an output of 1 and thus be different from B.

- The Moore model for a sequence recognizer usually has more states than the Mealy model.

#### **Example: Moore Model** (continued)

- We mark outputs on states for Moore model

- Arcs now show only state transitions

- Add a new state E to produce the output 1

- Note that the new state, E produces the same behavior in the future as state B. But it gives a different output at the present time. Thus these states do represent a different abstraction of the input history.

Chapter 6 - Part 2 19

D/0

#### **Example: Moore Model (continued)**

- The state table is shown below

- Memory aid re more state in the Moore model: "Moore is More."

| <b>1</b> 000 | $\bigcap_{1 \leq i \leq n} \mathbb{I}_{0 \leq n}$ |

|--------------|---------------------------------------------------|

| A/0 $B/0$    | C/0 $D/0$                                         |

| 0            | E/1                                               |

|              | 0                                                 |

| Present | Next State | Output |

|---------|------------|--------|

| State   | x=0 $x=1$  | y      |

| A       | A B        | 0      |

| В       | A C        | 0      |

| C       | D C        | 0      |

| D       | A E        | 0      |

| E       | A C        | 1      |

ogic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Pearson Education, Inc.

### **State Assignment – Example 1**

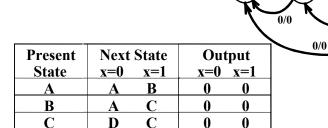

| Present | Next State |     | Next State |     | Out | tput |

|---------|------------|-----|------------|-----|-----|------|

| State   | x=0        | x=1 | x=0        | x=1 |     |      |

| A       | A          | В   | 0          | 0   |     |      |

| В       | A          | В   | 0          | 1   |     |      |

- How may assignments of codes with a minimum number of bits?

- Two -A = 0, B = 1 or A = 1, B = 0

- Does it make a difference?

- Only in variable inversion, so small, if any.

Logic and Computer Dealgn Fundamentale PowerPoint® Slides © 2004 Poursun Education, Inc.

Chapter 6 - Part 2 21

# **State Assignment – Example 2**

| Present | Next State |     | Out | tput |

|---------|------------|-----|-----|------|

| State   | x=0        | x=1 | x=0 | x=1  |

| A       | A          | В   | 0   | 0    |

| В       | A          | C   | 0   | 0    |

| C       | D          | С   | 0   | 0    |

| D       | A          | В   | 0   | 1    |

- How may assignments of codes with a minimum number of bits?

- $4 \times 3 \times 2 \times 1 = 24$

- Does code assignment make a difference in cost?

### **State Assignment – Example 2** (continued)

- Assignment 1: A = 0.0, B = 0.1, C = 1.0, D = 1.1

- The resulting coded state table:

| Present | Next State      |     | Out   | put   |

|---------|-----------------|-----|-------|-------|

| State   | $x = 0 \ x = 1$ |     | x = 0 | x = 1 |

| 0.0     | 0 0             | 0 1 | 0     | 0     |

| 0 1     | 0 0             | 10  | 0     | 0     |

| 1 0     | 11              | 10  | 0     | 0     |

| 1 1     | 0 0             | 0 1 | 0     | 1     |

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Stites © 2864 Peerson Education, Inc.

Chapter 6 - Part 2 23

# **State Assignment – Example 2** (continued)

- Assignment 2: A = 0 0, B = 0 1, C = 1 1, D = 1 0

- The resulting coded state table:

| Present | Next            | State | Out              | put   |

|---------|-----------------|-------|------------------|-------|

| State   | $x = 0 \ x = 1$ |       | $\mathbf{x} = 0$ | x = 1 |

| 0 0     | 0 0             | 0 1   | 0                | 0     |

| 0 1     | 0 0             | 1 1   | 0                | 0     |

| 1 1     | 10              | 1 1   | 0                | 0     |

| 10      | 0 0             | 0 1   | 0                | 1     |

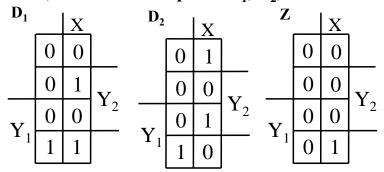

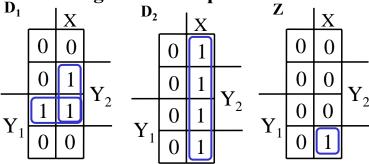

#### Find Flip-Flop Input and Output **Equations: Example 2 - Assignment 1**

- Assume D flip-flops

- Interchange the bottom two rows of the state table, to obtain K-maps for D<sub>1</sub>, D<sub>2</sub>, and Z:

Chapter 6 - Part 2 25

#### **Optimization: Example 2: Assignment 1**

Performing two-level optimization:

$Z = XY_1Y_2$

**Gate Input Cost = 22**

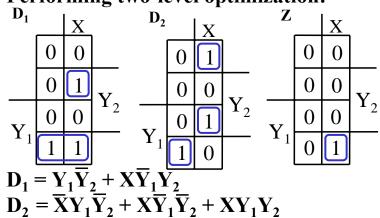

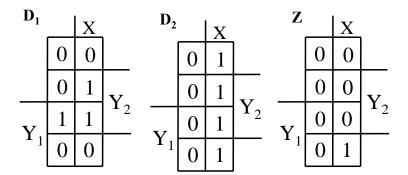

#### Find Flip-Flop Input and Output **Equations: Example 2 - Assignment 2**

- Assume D flip-flops

- Obtain K-maps for D<sub>1</sub>, D<sub>2</sub>, and Z:

PowerPoint<sup>®</sup> Stides © 2004 Peerson Education, Inc.

Chapter 6 - Part 2 27

# **Optimization: Example 2: Assignment 2**

Performing two-level optimization:

$\mathbf{D}_1 = \mathbf{Y}_1 \mathbf{Y}_2 + \mathbf{X} \overline{\mathbf{Y}}_2$ **Gate Input Cost = 9** Select this state assignment for  $D_2 = X$

$Z = XY_1\overline{Y}_2$  completion of the design

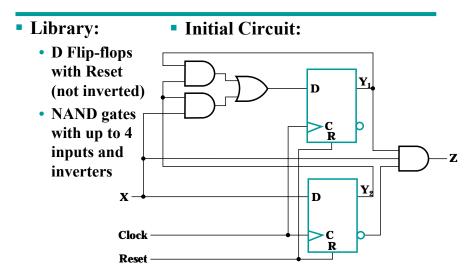

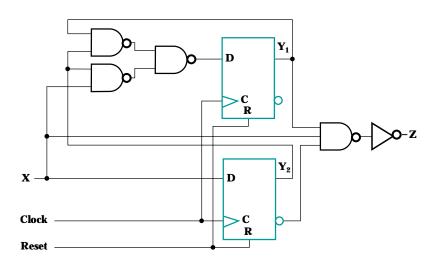

# **Map Technology**

Logis and Computer Dealgn Fundamentals PowerPoint® Stides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 29

# **Mapped Circuit - Final Result**

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Poerson Education, Inc.

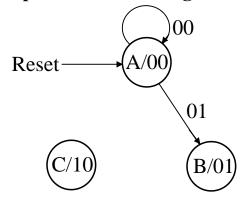

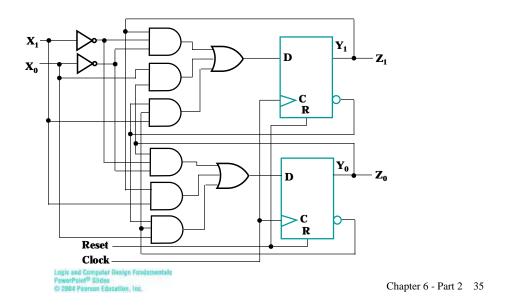

#### **Sequential Design: Example 3**

- Design a sequential modulo 3 accumulator for 2bit operands

- Definitions:

- Modulo *n* adder an adder that gives the result of the addition as the remainder of the sum divided by n

- Example: 2 + 2 modulo 3 = remainder of 4/3 = 1

- Accumulator a circuit that "accumulates" the sum of its input operands over time - it adds each input operand to the stored sum, which is initially 0.

- Stored sum:  $(Y_1,Y_0)$ , Input:  $(X_1,X_0)$ , Output:  $(Z_1,Z_0)$

Chapter 6 - Part 2 31

#### **Example 3 (continued)**

Complete the state diagram:

# **Example 3 (continued)**

#### Complete the state table

| $X_1X_0$ | 00          | 01          | 11          | 10          | $Z_1Z_0$ |

|----------|-------------|-------------|-------------|-------------|----------|

| $Y_1Y_0$ |             |             |             |             | 1 0      |

|          | $Y_1(t+1),$ | $Y_1(t+1),$ | $Y_1(t+1),$ | $Y_1(t+1),$ |          |

|          | $Y_0(t+1)$  | $Y_0(t+1)$  | $Y_0(t+1)$  | $Y_0(t+1)$  |          |

| A (00)   | 00          |             | X           |             | 00       |

| B (01)   |             |             | X           |             | 01       |

| - (11)   | X           | X           | X           | X           | 11       |

| C (10)   |             |             | X           |             | 10       |

- State Assignment:  $(Y_1, Y_0) = (Z_1, Z_0)$

- Codes are in gray code order to ease use of K-maps in the next step

Logic and Computer Design Fundamentals PowerPoint® Sides © 2004 Paerson Education, Inc.

Chapter 6 - Part 2 33

# **Example 3 (continued)**

Find optimized flip-flop input equations for D flip-flops

| $\mathbf{D}_1$ | $\mathbf{D}_1$ |   |           | $X_1$ |                |  |

|----------------|----------------|---|-----------|-------|----------------|--|

|                |                |   | X         |       |                |  |

|                |                |   | X         |       | v              |  |

| v              | X              | X | X         | X     | $\mathbf{Y}_0$ |  |

| $\mathbf{Y}_1$ |                |   | X         |       |                |  |

|                |                | Σ | $\zeta_0$ |       |                |  |

| $\mathbf{D}_0$ |   |   | X                    | ·<br>1 |                |

|----------------|---|---|----------------------|--------|----------------|

|                |   |   | X                    |        |                |

|                |   |   | X                    |        | v              |

| v              | X | X | X                    | X      | $\mathbf{Y}_0$ |

| $\mathbf{Y}_1$ |   |   | X                    |        |                |

| ,              |   | Σ | $\overline{\zeta_0}$ |        | •              |

- $\mathbf{D}_1 =$

- $D_0 =$

#### Circuit - Final Result with AND, OR, NOT

#### **Other Flip-Flop Types**

- J-K and T flip-flops

- Behavior

- Implementation

- Basic descriptors for understanding and using different flip-flop types

- Characteristic tables

- Characteristic equations

- Excitation tables

- For actual use, see Reading Supplement Design and Analysis Using J-K and T Flip-Flops

#### J-K Flip-flop

#### Behavior

- Same as S-R flip-flop with J analogous to S and K analogous to R

- Except that J = K = 1 is allowed, and

- For J = K = 1, the flip-flop changes to the *opposite* state

- As a master-slave, has same "1s catching" behavior as S-R flip-flop

- If the master changes to the wrong state, that state will be passed to the slave

- E.g., if master falsely set by J = 1, K = 1 cannot reset it during the current clock cycle

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Stidss © 2004 Poerson Education, Inc.

Chapter 6 - Part 2 37

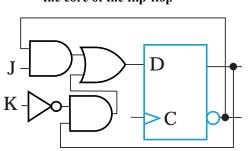

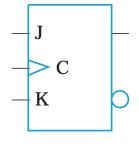

#### **J-K Flip-flop (continued)**

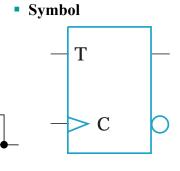

#### Implementation

To avoid 1s catching behavior, one solution used is to use an edge-triggered D as the core of the flip-flop

#### Symbol

#### T Flip-flop

- Behavior

- Has a single input T

- For T = 0, no change to state

- For T = 1, changes to opposite state

- Same as a J-K flip-flop with J = K = T

- As a master-slave, has same "1s catching" behavior as J-K flip-flop

- Cannot be initialized to a known state using the T input

- Reset (asynchronous or synchronous) essential

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Stidss © 2004 Poerson Education, Inc.

Chapter 6 - Part 2 39

# T Flip-flop (continued)

#### **Basic Flip-Flop Descriptors**

- Used in analysis

- Characteristic table defines the next state of the flip-flop in terms of flip-flop inputs and current state

- Characteristic equation defines the next state of the flip-flop as a Boolean function of the flip-flop inputs and the current state

- Used in design

- Excitation table defines the flip-flop input variable values as function of the current state and next state

Logic and Computer Dealgn Funda: PowerPoint® Slides © 2004 Pearson Education, Inc.

Chapter 6 - Part 2 41

#### **D Flip-Flop Descriptors**

Characteristic Table

| D | Q(t+1) | Operation |

|---|--------|-----------|

| 0 | 0      | Reset     |

| 1 | 1      | Set       |

Characteristic Equation

$$\mathbf{Q(t+1)} = \mathbf{D}$$

Excitation Table

| Q(t+1) | D | Operation |

|--------|---|-----------|

| 0      | 0 | Reset     |

| 1      | 1 | Set       |

# **T Flip-Flop Descriptors**

Characteristic Table

| T | Q(t+1)            | Operation  |  |

|---|-------------------|------------|--|

| 0 | Q(t)              | No change  |  |

| 1 | $\overline{Q}(t)$ | Complement |  |

Characteristic Equation

$$Q(t+1) = T \oplus Q$$

Excitation Table

| Q(t+1)            | T | Operation  |

|-------------------|---|------------|

| Q(t)              | 0 | No change  |

| $\overline{Q}(t)$ | 1 | Complement |

Logic and Computer Design Fundamental PowerPoint<sup>®</sup> Slides

© 2004 Pearson Education, Inc.

Chapter 6 - Part 2 43

### **S-R Flip-Flop Descriptors**

Characteristic Table

| S | R | Q(t+1) | Operation |

|---|---|--------|-----------|

| 0 | 0 | Q(t)   | No change |

| 0 | 1 | 0      | Reset     |

| 1 | 0 | 1      | Set       |

| 1 | 1 | ?      | Undefined |

Characteristic Equation

$$Q(t+1) = S + \overline{R}Q, S \cdot R = 0$$

Excitation Table

| Q(t) | Q(t+1) | S R | Operation                 |

|------|--------|-----|---------------------------|

| 0    | 0      | 0 X | No change<br>Set<br>Reset |

| 0    | 1      | 1 0 | Set                       |

| 1    | 0      | 0 1 | Reset                     |

| 1    | 1      | X 0 | No change                 |

Logic and Computer Dealgn Fundamentals PowerPoint<sup>®</sup> Stidss

#### **J-K Flip-Flop Descriptors**

Characteristic Table

| J | K | Q(t+1)            | Operation  |

|---|---|-------------------|------------|

| 0 | 0 | Q(t)              | No change  |

| 0 | 1 | 0                 | Reset      |

| 1 | 0 | 1                 | Set        |

| 1 | 1 | $\overline{Q}(b)$ | Complement |

• Characteristic Equation

$$Q(t+1) = J \overline{Q} + \overline{K} Q$$

Excitation Table

| $\mathbf{Q}(\mathbf{t})$ | Q(t+1) | J K | Operation                 |

|--------------------------|--------|-----|---------------------------|

| 0                        | 0      | 0 X | No change                 |

| 0                        | 1      | 1 X | Set<br>Reset<br>No Change |

| 1                        | 0      | X 1 | Reset                     |

| 1                        | 1      | X 0 | No Change                 |

Logic and Computer Dealgn Fundament: PowerPoint® Slides

2004 Pearson Education, Inc.

Chapter 6 - Part 2 45

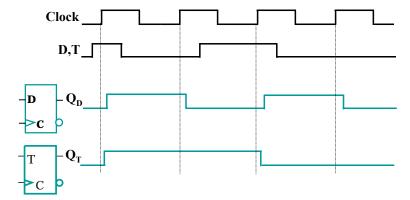

#### Flip-flop Behavior Example

Use the characteristic tables to find the output waveforms for the flip-flops shown:

Logic and Computer Dealgn Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Poerson Education, Inc.

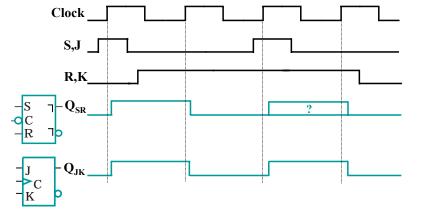

# Flip-Flop Behavior Example (continued)

Use the characteristic tables to find the output waveforms for the flip-flops shown:

Logic and Computer Design Fundamentals PowerPoint<sup>®</sup> Slides © 2004 Passau Education, inc.

Chapter 6 - Part 2 47

#### Terms of Use

- © 2004 by Pearson Education, Inc. All rights reserved.

- The following terms of use apply in addition to the standard Pearson Education <u>Legal Notice</u>.

- Permission is given to incorporate these materials into classroom presentations and handouts only to instructors adopting Logic and Computer Design Fundamentals as the course text.

- Permission is granted to the instructors adopting the book to post these

materials on a protected website or protected ftp site in original or

modified form. All other website or ftp postings, including those

offering the materials for a fee, are prohibited.

- You may not remove or in any way alter this Terms of Use notice or any trademark, copyright, or other proprietary notice, including the copyright watermark on each slide.

- Return to Title Page