## Name **Student ID:**

## Digital Systems II (A-B), Midterm I

## <u>90 minutes</u>

- 1. Consider the state table that represents a sequential circuit with one input X and one output Z.

- Is this a Moore or Mealy machine? Explain briefly. (03 pts) a)

- Sketch the waveform for the flip-flop outputs A and B b) referring to the state table. Assume that A=B=0 and the output Z=0 initially. The flip-flops are triggered at the positive edge. (12 pts)

|     | Present |   | Next State |   |     |   | Output | a) |      |      |  |      |   |  |

|-----|---------|---|------------|---|-----|---|--------|----|------|------|--|------|---|--|

|     | State   |   | X=0        |   | X=1 |   |        |    |      |      |  |      |   |  |

|     | Α       | В | Α          | В | Α   | В | Z      |    |      |      |  |      |   |  |

|     | 0       | 0 | 0          | 0 | 0   | 1 | 0      |    |      |      |  |      |   |  |

|     | 0       | 1 | 0          | 1 | 1   | 0 | 1      |    |      |      |  |      |   |  |

|     | 1       | 0 | 1          | 1 | 1   | 0 | 1      |    |      |      |  |      |   |  |

|     | 1       | 1 | 0          | 0 | 1   | 0 | 0      |    |      |      |  |      |   |  |

|     |         |   |            |   |     |   |        |    |      |      |  |      |   |  |

|     | b)      |   |            |   |     |   |        |    |      |      |  |      | - |  |

| CLI | ĸſ      |   |            |   |     |   |        | [  |      |      |  |      |   |  |

|     |         |   |            |   |     |   |        |    |      | <br> |  |      |   |  |

| NZ. |         |   |            |   |     |   |        |    |      |      |  |      |   |  |

| X   |         |   |            |   |     |   |        |    |      | <br> |  |      |   |  |

|     |         |   |            |   |     |   |        |    | <br> |      |  | <br> |   |  |

| A   |         |   |            |   |     |   |        |    | <br> |      |  |      |   |  |

|     |         |   |            |   |     |   |        |    | <br> |      |  |      |   |  |

|     |         |   |            |   |     |   |        |    |      |      |  |      |   |  |

| B   |         |   |            |   |     |   |        |    |      |      |  |      |   |  |

|     |         |   |            |   |     |   |        |    |      |      |  |      |   |  |

| Ζ   |         |   |            |   |     |   |        |    |      |      |  |      |   |  |

- 2. A JN flip-flop has two inputs J and N. Input J behaves like the J input of JK flip-flop. N behaves like the complement of the K input of JK flip-flop (that is N=K).

- a) Obtain the characteristic table of JN flip-flop. (07 pts)

- b) Derive the excitation table of the flip-flop.(08 pts)

| 1 | , |  |

|---|---|--|

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

|   |   |  |

April 07, 2005

| 1 |  |

|---|--|

| 2 |  |

| 3 |  |

| 4 |  |

| 5 |  |

|   |  |

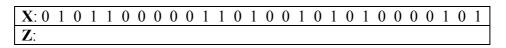

- 3. Design a sequence detector with one input X and one output Z. Every time the input "1 0 1" is detected the output Z=1. However, the detector needs to be first activated with a key, i.e. it has to receive at least three consecutive 0's before it will start detecting the desired sequence "1 0 1". Once the key has been received, the sequence detector keeps looking for the desired sequence. Overlapping sequences are allowed.

- a) For the following input sequence give the output sequence (05 pts)

b) Give the state diagram of the sequence detector including the key detection. Assume that the circuit is a <u>Mealy machine</u>. (20 pts)

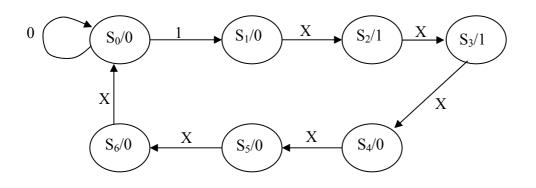

4. Consider the following state diagram that represents a sequential circuit with one input X and one output Z. Design the circuit with <u>D flip-flops</u>. Give the state table, derive the logic equations for the inputs to the flip-flops and for the output function. Assume that the states are encoded as follows: <u>S<sub>0</sub>(000), S<sub>1</sub>(001), S<sub>2</sub>(010), S<sub>3</sub>(011)</u>, etc. X: don't care (25 pts)

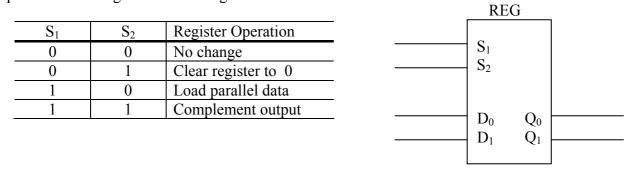

5. Draw the logic diagram of a <u>2-bit register with mode selection inputs  $S_1$  and  $S_2$ . The register is to be operated according to the following function table:</u>

Use JK flip-flops in the register. Use only the inputs J and K to perform the listed operation. (20 pts)